Verilog HDL Code for BCD and Gray Counters

Advertisement

This document presents Verilog HDL code for both a BCD counter and a Gray counter.

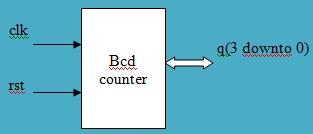

BCD Counter

Symbol

Truth Table

| Rst | Clk | Q |

|---|---|---|

| 1 | X | 0000 |

| 0 | 1 | 0001 |

| 0 | 1 | 0010 |

| 0 | 1 | 0011 |

| 0 | 1 | 0100 |

| 0 | 1 | 0101 |

| 0 | 1 | 0110 |

| 0 | 1 | 0111 |

| 0 | 1 | 1000 |

| 0 | 1 | 1001 |

Verilog Code

module bcd(clr, clk, dir, tc, q);

input clr, clk, dir;

output reg tc;

output reg[3:0] q;

always @(posedge clk, posedge clr) begin

if (clr == 1)

q = 4'd0;

else begin

if (dir == 1)

q = q + 1;

else if (dir == 0)

q = q - 1;

if (dir == 1 & q == 4'd10) begin

q = 4'd0;

tc = 1'b1;

end else if (dir == 0 & q == 4'd15) begin

q = 4'd9;

tc = 1'b1;

end else

tc = 1'b0;

end

end

endmodule

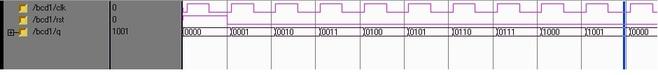

Simulation Result

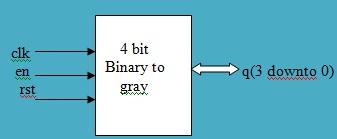

Gray Counter

Symbol

Truth Table

| Rst | Clk | En | B3 | B2 | B1 | B0 | G3 | G2 | G1 | G0 |

|---|---|---|---|---|---|---|---|---|---|---|

| 1 | X | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

| 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

Verilog Code

module gray(clr, clk, q);

input clr, clk;

output reg[2:0] q;

reg temp=3'd0;

always @(posedge clk, posedge clr) begin

if (clr == 0) begin

case(temp)

3'd0: q=3'd1;

3'd1: q=3'd3;

3'd2: q=3'd6;

3'd3: q=3'd2;

3'd6: q=3'd7;

3'd7: q=3'd5;

3'd5: q=3'd4;

3'd4: q=3'd0;

endcase

end else

q=3'd0;

end

endmodule

Advertisement

RF

RF