Dominant vs Recessive Bit : CAN Bus Key Differences

Advertisement

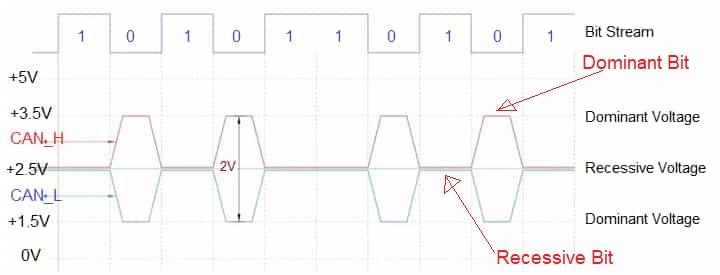

Introduction : The concepts of dominant and recessive bits are the absolute foundation of how the Controller Area Network (CAN) works. They are not just simple representations of ‘0’ and ‘1’; their physical properties are what enable CAN’s most critical features, like collision free arbitration and error signaling.

What is “Wired-AND” logic

- CAN bus behaves like a “Wired-AND” circuit. This means as follows.

- If any one node on the bus sends a dominant bit, the entire bus becomes dominant.

- The bus can only be in a recessive state if all nodes on the bus are sending a recessive bit.

Dominant Bit

- Logic level : Represents a logic ‘0’.

- Physical bus state : CAN High (CAN_H) is driven towards ~ 3.5V. CAN Low (CAN_L) is driven towards ~ 1.5V.

- Voltage difference : High (Vdiff = CAN_H - CAN_L = ~ 2.0V).

- Transceiver action : Actively drives the bus lines apart.

- Bus “Energy” : Requires power to create the voltage difference.

Recessive Bit

- Logic level : Represents a logic ‘1’.

- Physical bus state : The bus is not actively driven. Termination resistors pull both lines towards a resting voltage of ~ 2.5V.

- Voltage difference : Near Zero (Vdiff = CAN_H - CAN_L = ~ 0V).

- Transceiver action : Is passive; goes into a high-impedance state.

- Bus “Energy” : Is the bus’s default, unpowered or idle state.

Arbitration Rule

- If a node sends a recessive bit (1) but reads a dominant bit (0) on the bus, it means another node with a lower ID (and thus a ‘0’ in that bit position) is also transmitting.

- The node that sent the recessive bit instantly recognizes it has lost arbitration. It immediately stops transmitting and switches to being a receiver.

- The Winner: The node that sent the dominant bit continues transmitting, unaware there was ever a conflict.

Usage/Application

The dominant/recessive concept is used in every aspect of CAN communication.

| Usage Scenario | Dominant Bit (Logic ‘0’) | Recessive Bit (Logic ‘1’) |

|---|---|---|

| Data Transmission | Represents a ‘0’ in the Identifier, Data, CRC, and other fields of the message frame. | Represents a ‘1’ in the message frame. Also serves as the bus’s idle state. |

| Arbitration | Winning Bit: Overwrites a recessive bit to assert priority during arbitration. | Losing Bit: A node sending a recessive bit will lose arbitration if another node sends a dominant one. |

| Acknowledgement (ACK) | Confirms Receipt: A receiving node drives the bus dominant during the ACK slot to signal to the transmitter that the message was received correctly. | Signals No Receipt: The transmitter sends a recessive bit in the ACK slot. If it remains recessive, it means no node acknowledged the message. |

| Error Signaling | Error Frame: When a node detects an error, it transmits a sequence of 6 dominant bits. This is a powerful signal that intentionally violates protocol rules to get the attention of all other nodes, causing them to discard the current message. | Error Passive State: A node that is in an “error passive” state is not allowed to send dominant Error Frames, so as not to paralyze the bus. |

Summary: This logic ensures that when multiple nodes transmit simultaneously, the node with the higher priority (lower ID, more dominant bits) wins. This mechanism offers deterministic, efficient and reliable bus arbitration essential for real time automotive and embedded applications.

Advertisement

RF

RF