JESD204B vs JESD204C: Key Differences Compared

Advertisement

This page compares JESD204B and JESD204C, highlighting the key differences between these high-speed interface specifications.

Introduction:

JESD204B and JESD204C are high-speed interface specifications published by JEDEC (Joint Electron Devices Engineering Council). The specifications are designed to connect fast Analog-to-Digital Converters (ADCs) and Digital-to-Analog Converters (DACs) to high-speed FPGAs, processors, and ASICs. The three published specifications include JESD204A, JESD204B and JESD204C.

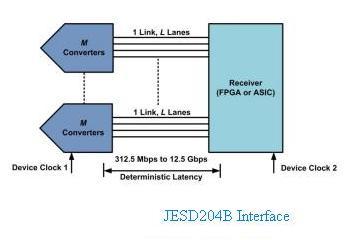

JESD204B

Here’s a breakdown of the features of JESD204B:

- Published in 2011, it’s an enhancement of the previous version, JESD204A.

- Device subclass 0 is backward compatible to JESD204A. Subclasses 1 and 2 are also supported.

- Supports speeds up to 12.5 Gbps, a significant improvement over the 3.125 Gbps supported by JESD204A.

- Supports single or multiple lanes, serial lane alignment and monitoring, and lane synchronization.

- Features a modular design that supports multi-device synchronization.

- Supports deterministic latency.

- Utilizes 8B/10B encoding, scrambling, and descrambling.

- For complete information, refer to the standard specifications published on jedec.org.

JESD204C

Following are the features of JESD204C:

- Backward compatible with JESD204A and JESD204B standard versions.

- Designed for high megabit and gigabit data rate applications in areas like 5G cellular equipment, test equipment, medical devices, and military applications.

- Builds upon all the features of JESD204B, adding new benefits.

- Supports device subclasses 0 and 1. Subclass-0 offers no deterministic latency. Subclass-1 uses a SYSREF signal to achieve deterministic latency.

- LEMC counter based on E range from 1 to 256.

- Uses 64/66 encoding, scrambling and descrambling.

- No FEC support.

- For complete information, refer to the standard specifications published on jedec.org.

Tabular Comparison: JESD204B vs JESD204C

The following table highlights the key differences between JESD204B and JESD204C:

| Features | JESD204B | JESD204C |

|---|---|---|

| Release year | 2011 | 2017 |

| Data Rate (Maximum) | 12.5 Gb/sec | 32.5 Gb/sec |

| Encoding schemes | 8B/10B | 8B/10B, 64B/66B, 64B/80B |

| DC Balance | Good | Better than JESD204B |

| Clock recovery | Good | Better than JESD204B |

| Data alignment | Good | Better than JESD204B |

| Bit Overhead | 25% | 3.125%, Much smaller than JESD204B |

| Scrambling polynomial | 1 + X14 + X15 | 1 + X39 + X58 |

| CRC encoding / Decoding | Not supported | Supported, CRC-12 is used to compute parity bits |

| Deterministic latency | Supported, in terms of RBD frame cycles | Supported, in terms of number of RBD characters |

| Transceiver classes | Not supported | Supported |

| SYNC | • Timing of SYNC~ signal are relative to frame clock • Supports hard wired SYNC interface | • Timing of SYNC~ signal are relative to sync generation and sync detection clocks • Supports hard wired and soft SYNC interface |

| Phase synchronization | • Same as JESD204A, except synchronous to local multi-frame clock (LMFC) instead of frame clock • SYSREF (subclass-1); SYNC (subclass-2) | • LMFC (local multi-frame clock), Local Extended multi-block clock • SYSREF (subclass-1 : 8B/10B, 64B/66B, 64B/80B); SYNC (subclass-2 : 8B/10B) |

| Maximum K frames in multi-frame | 32 | 256 |

| Programmable ILAS length | Supported | Not supported (Fixed to 4) |

Advertisement

RF

RF