M-PHY Interface: Protocol and Advantages

Advertisement

This page describes the basics of the M-PHY (MIPI Physical Layer) protocol and its advantages.

Introduction

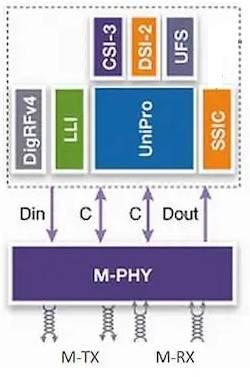

M-PHY is a physical layer protocol developed for DigRFv4, LLI, Unipro, CSI-3, and DSI-2 protocols by the MIPI Alliance. It also supports the UFS protocol standard developed by JEDEC and the SSIC protocol standard developed by USB-IF. M-PHY is commonly used in mobile devices like smartphones and tablets for chip-to-chip communication.

The MIPI Alliance develops hardware and software interface specifications for mobile devices. Popular physical layer standards include C-PHY, D-PHY, M-PHY, HSI, Slimbus, DigRF, etc. M-PHY is considered the successor to the D-PHY layer.

Both M-PHY and D-PHY physical layers are designed to be reusable and scalable for different components within a mobile terminal. Different versions of the M-PHY specifications have been released, including versions 2.0, 3.0, 4.1, and 5.0.

What is M-PHY?

The M-PHY interface supports data rates exceeding 5 Gbps. It embeds the clock signal within the data frame using 8b/10b encoding.

It’s an optical-friendly interface that supports data transfer in two modes: burst mode and continuous mode. It also supports both High Speed (HS) and Low Speed (LS) modes. The low-speed mode accommodates both PWM (Pulse Width Modulation) and NRZ (Non-Return to Zero) signaling. It supports both large and small amplitude drive strengths and includes two types of modules (Type-I and Type-II).

As the figure illustrates, an M-PHY link consists of at least two uni-directional lanes. Each lane comprises an M-TX module that communicates with an M-RX module on another chip via two differential lines. These differential lines carry both HS and LS signals.

Here are some features of the M-PHY physical layer protocol developed by the MIPI Alliance:

- Supports signaling speeds from 10 kbit/sec to 11.6 Gbit/sec per lane and supports 1-4 lanes

- Serial interface with embedded clock using 8b10b symbol encoding/decoding scheme

- M-PHY supports various states viz. LS burst, HS burst, STALL, HIBERN8 and SLEEP

- Supports Type-I and Type-II LS modes

Benefits or Advantages of M-PHY Layer

The following are the benefits and advantages of using the M-PHY layer:

- Improved Performance and Power Management: Offers significant improvements in both areas.

- Robust Against RF Interference: Designed to be resistant to RF interference and generates low RF emissions.

- Power Saving Features: Utilizes low power modes, switchable termination, and programmable low amplitude for optimized power consumption.

- High Speed: Achieves high speeds exceeding 5 Gbps using differential signaling.

- Fewer Signal Wires: Requires fewer signal wires (and therefore, fewer pins) because it uses 8b/10b encoding, which embeds the clock signal within the data.

- More Bandwidth per Pin: Provides more bandwidth per pin and improved power efficiency.

- Flexible Bandwidth Support: Supports a variable number of links/sub-links/data lanes to enable flexible bandwidth allocation.

Advertisement

RF

RF