Verilog Code for Half Adder, Half Subtractor, and Full Subtractor

Advertisement

This page provides Verilog HDL code for a half adder, half subtractor, and full subtractor. Let’s dive into the details.

Half Adder

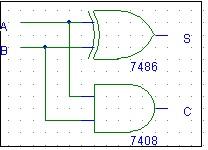

The half adder truth table and schematic (Fig. 1) are shown below.

The boolean expressions are:

- Sum (S) = A XOR B ()

- Carry (C) = A AND B ()

Half Adder Truth Table

| Input A | Input B | Output S | Output C |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

Half Adder Schematic

Half Adder Verilog Code

module ha ( a, b, s, c);

input a, b;

output s, c;

assign s = a ^ b;

assign c = a & b;

endmodule

Half Subtractor

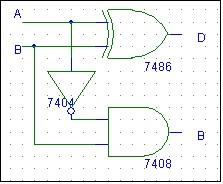

The half subtractor truth table and schematic (Fig. 2) are provided below.

The boolean expressions are:

- Difference (D) = A XOR B ()

- Borrow (Br) = NOT A AND B ()

Half Subtractor Truth Table

| Input A | Input B | Output D | Output Br |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

Half Subtractor Schematic

Half Subtractor Verilog Code

module hs ( a, b, d, br);

input a, b;

output d, br;

assign d = a ^ b;

assign br = ~a & b;

endmodule

Full Subtractor

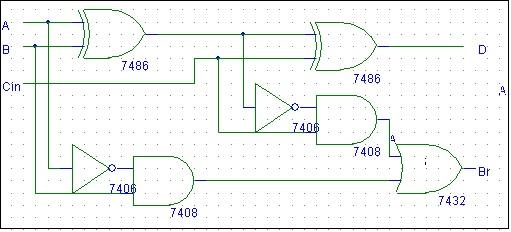

The full subtractor truth table and schematic (Fig. 3) are mentioned below.

The boolean expressions are:

- Difference (D) = A XOR B XOR Cin ()

- Borrow (Br) = (NOT A AND B) OR (B AND Cin) OR (NOT A AND Cin) ()

Full Subtractor Truth Table

| Input A | Input B | Input Cin | Output D | Output Br |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

Full Subtractor Schematic

Full Subtractor Verilog Code

module fs ( a, b, c, d, br);

input a, b, c;

output d, br;

assign d = a ^ b ^ c;

assign br=(( ~a)& (b ^ c)) | (b & c);

endmodule

Advertisement

RF

RF