8 to 1 Multiplexer Verilog HDL Code

Advertisement

This page provides the Verilog HDL code for an 8-to-1 Multiplexer.

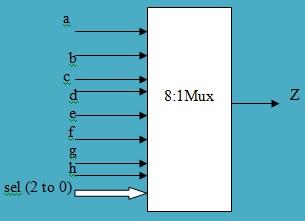

Symbol

Below is the symbol of the 8-to-1 Multiplexer.

Truth Table

Here’s the truth table for the 8-to-1 Multiplexer:

| Sel2 | Sel1 | Sel0 | Z |

|---|---|---|---|

| 0 | 0 | 0 | A |

| 0 | 0 | 1 | B |

| 0 | 1 | 0 | C |

| 0 | 1 | 1 | D |

| 1 | 0 | 0 | E |

| 1 | 0 | 1 | F |

| 1 | 1 | 0 | G |

| 1 | 1 | 1 | H |

Verilog Code

module mux8_1 (

input [7:0] I,

input [2:0] S,

input en,

output reg y

);

always @(en, S, I, y)

begin

if (en == 1)

begin

if (S == 3'b000)

y = I[0];

else if (S == 3'b001)

y = I[1];

else if (S == 3'b010)

y = I[2];

else if (S == 3'b011)

y = I[3];

else if (S == 3'b100)

y = I[4];

else if (S == 3'b101)

y = I[5];

else if (S == 3'b110)

y = I[6];

else if (S == 3'b111)

y = I[7];

end

else

y = 0;

end

endmodule

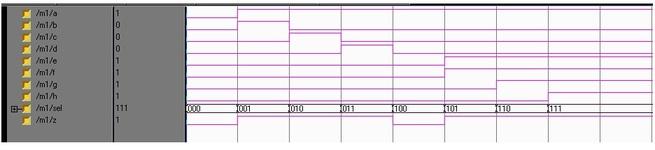

Simulation Result

Here’s a simulation result image showing the behavior of the 8-to-1 Multiplexer:

Advertisement

RF

RF