4-to-1 Multiplexer and 1-to-4 Demultiplexer Verilog Code

Advertisement

This page provides Verilog HDL code for a 4-to-1 multiplexer and a 1-to-4 demultiplexer.

4 to 1 Multiplexer

Here’s the information for a 4-to-1 multiplexer:

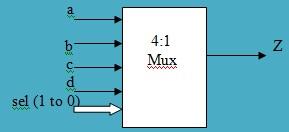

Symbol:

Truth Table:

| Sel1 | Sel0 | Z |

|---|---|---|

| 0 | 0 | a |

| 0 | 1 | b |

| 1 | 0 | c |

| 1 | 1 | d |

Verilog Code:

module mux4_1(I0,I1,I2,I3,s2,s1,y,en);

input I0,I1,I2,I3,s2,s1,en;

output y;

assign y <= ((~s2)&(~s1)&en&I0)| ((~s2)&(s1)&en&I1)|(s2&(~s1)&en&I2)|(s2&s1&en&I3);

endmodule

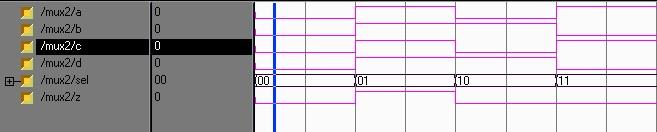

Simulation Result:

1 to 4 De-multiplexer

Now, let’s move on to the 1-to-4 de-multiplexer:

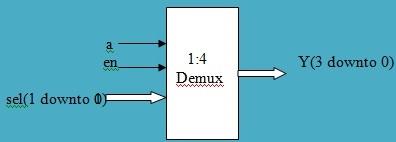

Symbol:

Truth Table:

| a | en | Sel1 | Sel0 | Y3 | Y2 | Y1 | Y0 |

|---|---|---|---|---|---|---|---|

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 1 | 0 | 0 | 0 | 1 |

| 0 | 1 | X | X | 0 | 0 | 0 | 0 |

Verilog Code:

module demux (s2,s1,I,en,y0,y1,y2,y3);

input s2,s1,I,en;

output y0,y1,y2,y3;

assign y0 = (~s2)&(~s1)& I& en;

assign y1 = (~s2)& s1& I& en;

assign y2 = s2&(~s1)& I & en;

assign y3 = s2& s1 & I & en;

endmodule

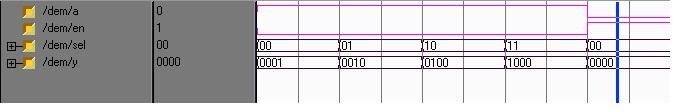

Simulation Result:

Advertisement

RF

RF