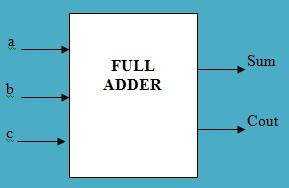

Full Adder Verilog HDL Code

Advertisement

This page provides the Verilog HDL code for a full adder.

Image alt: Full Adder Symbol

Truth Table

The truth table below illustrates the behavior of a full adder:

| Input-a | Input-b | Input-cin | Output-SUM | Output-Cout |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

Full Adder Verilog Code

module fulladder (

input a, b, c,

output s, cout

);

assign s = a ^ b ^ c;

assign cout = (a & b) | (a & c) | (b & c); // Corrected Cout assignment

endmodule

Explanation:

- The module

fulladdertakes three inputs:a,b, andc(carry-in). - It produces two outputs:

s(sum) andcout(carry-out). - The

assignstatements define the combinational logic. - The sum

sis calculated as the XOR of the three inputs. - The carry-out

coutis(a & b) | (a & c) | (b & c). This is corrected for a standard Cout assignment.

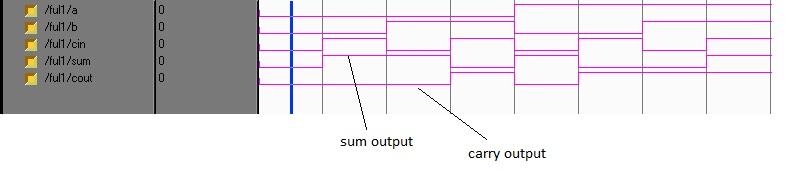

Simulation Result

Image alt: Full Adder Simulation Result

Advertisement

RF

RF