ARM Exception and Interrupt Controller

Advertisement

This ARM tutorial covers ARM exceptions and the interrupt controller.

ARM Vector Table

The following table outlines the ARM vector table:

| Exception/Interrupt | Shorthand | Address | High Address |

|---|---|---|---|

| Reset | RESET | 0x00000000 | 0xFFFF0000 |

| Undefined Instruction | UNDEF | 0x00000004 | 0xFFFF0004 |

| Software Interrupt | SWI | 0x00000008 | 0xFFFF0008 |

| Prefetch Abort | PABT | 0x0000000C | 0xFFFF000C |

| Data Abort | DABT | 0x00000010 | 0xFFFF0010 |

| Reserved | - | 0x00000014 | 0xFFFF0014 |

| Interrupt Request | IRQ | 0x00000018 | 0xFFFF0018 |

| Fast Interrupt Request | FIQ | 0x0000001C | 0xFFFF001C |

RESET

- Occurs when the processor powers up.

- Initializes the system and sets up stacks for different processor modes.

- Highest priority exception.

- Upon entry into the reset handler, the CPSR (Current Program Status Register) is in SVC (Supervisor) mode, and both IRQ and FIQ bits are set to 1, masking any interrupts.

DATA ABORT

- Second highest priority.

- Happens when the processor attempts to read/write to an invalid address or access with incorrect permissions.

- Upon entry into the Data Abort Handler, IRQs will be disabled (I-bit set to 1), and FIQs will be enabled. This means IRQs are masked, while FIQs remain unmasked.

FIQ

- Highest priority interrupt.

- IRQ & FIQs are disabled until the FIQ is handled.

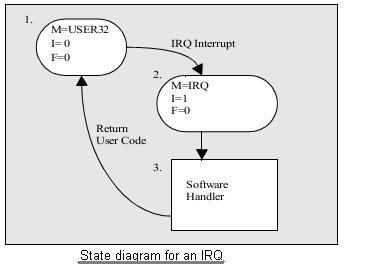

IRQ

- Second highest priority interrupt.

- The IRQ handler is entered only if there is no FIQ or Data Abort currently in progress.

Pre-Fetch Abort

- Similar to a data abort, but happens on address fetch failure.

- On entry to the handler, IRQs are disabled, but FIQs remain enabled and can occur during a Pre-Fetch abort.

SWI

- A Software Interrupt (SWI) exception occurs when the SWI instruction is executed and none of the other higher-priority exceptions have been flagged.

Undefined Instruction

- The Undefined Instruction exception occurs when an instruction not in the ARM or Thumb instruction set reaches the execute stage of the pipeline and none of the other exceptions have been flagged.

- It has the same priority as SWI, as only one can happen at a time. The instruction being executed cannot simultaneously be an SWI instruction and an undefined instruction.

ARM Exception Handling

The following events occur when an exception arises:

- The CPSR (Current Program Status Register) is stored in the SPSR (Saved Program Status Register) of the exception mode.

- The PC (Program Counter) is stored in the LR (Link Register) of the exception mode.

- The Link Register is set to a specific address based on the current instruction. For example, for an ISR (Interrupt Service Routine), LR = last executed instruction + 8.

- The CPSR is updated to reflect the exception.

- The PC is set to the address of the exception handler.

Advertisement

RF

RF