ARM Bus Technology, Memory, and Peripherals Explained

Advertisement

This ARM tutorial covers ARM bus technology, memory, and peripherals.

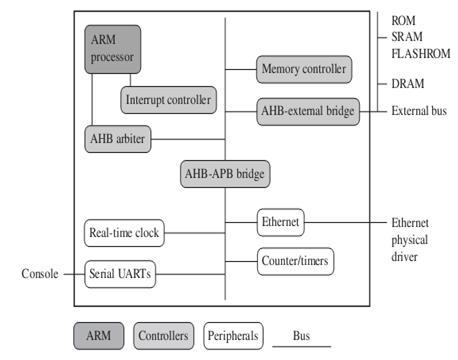

Embedded System Hardware

- An ARM processor controls the embedded device. An ARM processor comprises a core (the execution engine that processes instructions and manipulates data) plus the extensions interface it with a bus.

- Controllers coordinate important functional blocks of the system. Two commonly found controllers are interrupt and memory controllers.

- Peripherals provide all the input-output capability external to the chip and are responsible for the uniqueness of the embedded device.

- A Bus is used to communicate between different parts of the device.

ARM Bus Technology

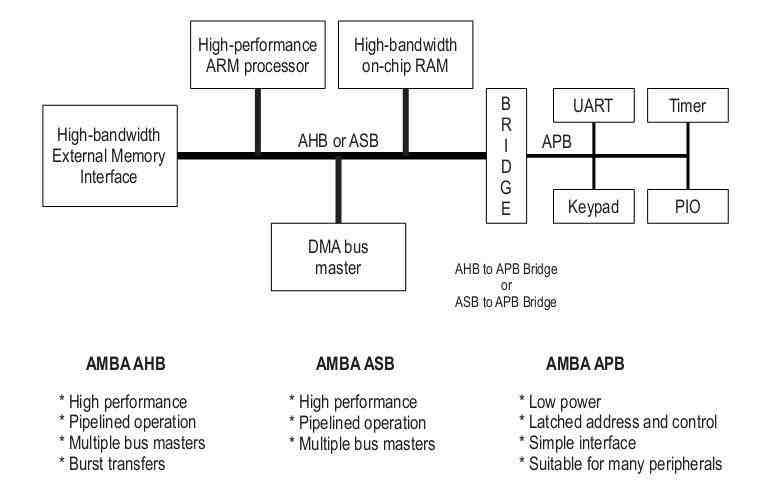

The AMBA specification defines an on-chip communication standard, used to design embedded microcontrollers with high performance. The ARM bus architecture typically utilizes the Advanced Microcontroller Bus Architecture (AMBA) standards, which include different bus protocols such as AHB (Advanced High-performance Bus), ASB (Advanced System Bus), and APB (Advanced Peripheral Bus). These protocols provide a structured and scalable communication framework for ARM-based systems.

Let us understand key components as shown in the ARM bus technology diagram. As shown, the ARM processor, high bandwidth memory, and on-chip RAM are connected via the high-performance AHB or AXI bus, ensuring rapid data access and processing. The DMA controller also uses this bus for efficient data transfers.

Components of ARM Bus Architecture

-

ARM Processor: The central processing unit (CPU) in the system, responsible for executing instructions and processing data. The ARM processor is usually connected to the high-performance AHB or AXI bus to ensure fast access to memory and other high-speed peripherals.

-

High Bandwidth Memory (HBM): High-performance memory designed for high data throughput. It is typically connected to the ARM processor via the AHB or AXI bus to support rapid data access and transfer. HBM is essential for applications requiring large data bandwidth, such as graphics processing and machine learning.

-

High Bandwidth On-chip RAM: On-chip RAM provides fast, low-latency storage for frequently accessed data. It is directly connected to the ARM processor through the high-speed AHB or AXI bus, ensuring quick data read/write operations essential for efficient processing.

-

DMA Bus Master: Direct Memory Access (DMA) controller acts as a bus master, capable of transferring data between memory and peripherals without involving the CPU. This reduces CPU overhead and increases data transfer efficiency. The DMA controller is connected to the AHB or AXI bus for high-speed data movement.

-

Bus Bridges: Bridges are used to connect different bus protocols within the system. For example, an AHB-to-APB bridge allows communication between high-speed AHB devices and lower speed APB peripherals. Bridges ensure seamless data transfer across different bus types.

-

AHB (Advanced High-performance Bus): AHB is a high-speed, high-bandwidth bus designed for connecting high-performance components like CPUs, high-speed memory, and DMA controllers. It supports burst transfers and provides efficient data throughput for demanding applications.

-

ASB (Advanced System Bus): ASB is an older, less common bus used for connecting system components. It provides a balance between performance and complexity, typically used in legacy designs.

-

APB (Advanced Peripheral Bus): APB is a low-power, low-bandwidth bus designed for connecting peripheral devices like UARTs, timers, PIOs, and keypads. It simplifies the interface for these devices and reduces power consumption.

-

UART (Universal Asynchronous Receiver/Transmitter): A peripheral device connected to the APB. UART is used for serial communication, enabling data exchange between the system and external devices. It is essential for debugging and communication in embedded systems.

-

Timer: A peripheral connected to the APB. Timers are used for generating time delays, measuring time intervals, and triggering periodic events. They are critical for real-time applications and system scheduling.

-

PIO (Programmable Input/Output): A peripheral connected to the APB. PIO provides configurable I/O pins that can be programmed to perform various input/output functions. Used for interfacing with external devices such as LEDs, switches, sensors and actuators. Each pin can be configured as an input or output and can often support various functions like interrupts or PWM.

-

Keypad: A peripheral device connected to the APB. Keypads provide user input capabilities, typically used in embedded systems for user interface purposes. The APB connection ensures low power consumption and sufficient bandwidth for keypad scanning and input detection.

ARM Memory

- Memory Width: Memory width is the number of bits the memory returns on each access—typically 8, 16, 32, or 64 bits. The memory width has a direct effect on the overall performance and cost ratio.

Following table covers fetching instructions from memory.

| Instruction size | 8 bit memory | 16 bit memory | 32 bit memory |

|---|---|---|---|

| ARM 32 bit | 4 cycles | 2 cycles | 1 cycle |

| Thumb 16 bit | 2 cycles | 1 cycle | 1 cycle |

Memory Types

-

ROM: Read-only memory (ROM) is the least flexible of all memory types because it contains an image that is permanently set at production time and cannot be reprogrammed. Devices use a ROM to hold boot code. Its main use is for holding the device firmware or storing long-term data that needs to be preserved after power is off.

-

DRAM: Dynamic random access memory (DRAM) is the most commonly used RAM for devices. It has the lowest cost per megabyte compared with other types of RAM. DRAM is dynamic - it needs to have its storage cells refreshed and given a new electronic charge every few milliseconds, so you need to set up a DRAM controller before using the memory.

-

SRAM: Static random access memory (SRAM) is faster than the more traditional DRAM but requires more silicon area. SRAM is static - the RAM does not require refreshing.

-

SDRAM: SDRAM stands for Synchronous Dynamic Random Access Memory. It is one of the DRAM types. It runs at a high clock speed compared to conventional memory. It gets synchronized with the processor bus as SDRAM is clocked.

ARM Peripherals

-

A peripheral device performs input and output functions for the chip by connecting to other devices or sensors that are off-chip.

-

All ARM peripherals are memory mapped - the programming interface is a set of memory-addressed registers. The address of these registers is an offset from a specific peripheral base address.

-

Controllers are specialized peripherals that implement higher levels of functionality within an embedded system.

-

Peripheral devices like UART, Timer, PIO, and Keypad are connected via the low-power APB. Data from these peripherals is transferred to the ARM processor or memory through the APB, potentially crossing an AHB-to-APB bridge if necessary.

ARM peripherals are hardware components that interface with the ARM processor to provide additional functionality beyond the core processing capabilities. These peripherals enable the system to interact with the external environment, perform specific tasks, and enhance overall system performance.

Various communication bus interfaces such as I2C, and SPI are used to interface peripherals with the ARM processor. Static Memory Controller (SMC) and Dynamic Memory Controller are used to interface SRAM and DRAM respectively.

Like PIOs there are GPIOs which also provide programmable pins that can be configured as input or output. GPIOs are used for simple on/off control of devices, reading the status of switches or sensors, and generating interrupt signals for events.

Memory Controllers

Memory controllers connect different types of memory to the processor bus. On power-up, a memory controller is configured in hardware to allow certain memory devices to be active. These memory devices allow the initialization code to be executed. Some memory devices must be set up by software; for example, when using DRAM, you first have to set up the memory timings and refresh rate before it can be accessed.

Interrupt Controllers

There are two types of interrupt controller available for the ARM processor:

-

Standard interrupt controller: The interrupt handler determines which device requires servicing by reading a device bitmap register in the interrupt controller.

-

Vector interrupt controller (VIC): Prioritizes interrupts and simplifies the determination of which device caused the interrupt. After associating a priority and a handler address with each interrupt, the VIC only asserts an interrupt signal to the core if the priority of a new interrupt is higher than the currently executing interrupt handler.

Advertisement

RF

RF