Barrel Shifter VHDL Code and Test Bench

Advertisement

This document provides VHDL code for a Barrel Shifter, along with a corresponding test bench. It also presents the simulated and synthesized outputs obtained using ModelSIM and Leonardo Spectrum tools, respectively.

The Barrel Shifter’s primary functions are:

- Rotating or shifting input data.

- Rotating the data by a specified number of bits in a combinational manner.

Barrel Shifter VHDL Code

This VHDL model implements a Barrel Shifter that rotates the input data by a specified number of bits.

-- Develop a VHDL model for a Barrel shifter that rotates

-- the input data by the specified number of bits.

library ieee;

use ieee.std_logic_1164.all;

entity Barrel is

port (

clk,reset,load :in std_logic;

data_in:in std_logic_vector (7 downto 0);

data_out:out std_logic_vector (7 downto 0)

);

end Barrel;

architecture Barrel of Barrel is

begin

process (reset,clk,data_in)

variable d: std_logic_vector (7 downto 0);

begin

if (reset = '0') then

d:=(others => '0');

elsif (clk'event and clk = '1') then

if (load ='1') then

d:=data_in;

else

d:= d(0) & d(7 downto 1) ;

end if;

end if;

data_out<= d;

end process;

end Barrel;

Barrel Shifter Test Bench in VHDL

The following code provides a test bench for the Barrel Shifter.

--test bench for barrel shifter

library ieee;

use ieee.std_logic_1164.all;

entity tb_Barrel is

end tb_Barrel;

architecture tb_Barrel of tb_Barrel is

component Barrel

port (

clk,reset,load :in std_logic;

data_in:in std_logic_vector (7 downto 0);

data_out:out std_logic_vector (7 downto 0)

);

end component;

signal clk,res,load : std_logic;

signal d_in,d_out : std_logic_vector (7 downto 0);

begin

br: Barrel port map (clk,res,load,d_in,d_out);

process

begin

res <= '1';

load <= '1';

wait for 5 ns;

load <= '1';

clk<='0';

d_in<="11111101";

wait for 5 ns;

clk<='1';

d_in<="11111111";

wait for 5 ns;

res <= '1';

d_in <= "01100101";

load <= '1';

wait for 5 ns;

load <= '0';

wait;

end process;

end tb_Barrel;

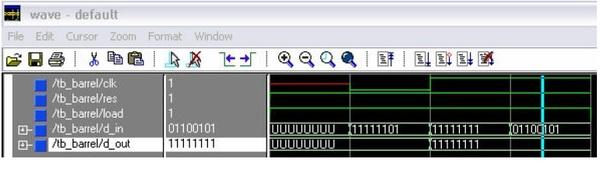

Simulated Output

The simulated output of the Barrel Shifter, obtained using ModelSIM, is shown below:

Figure 1: Simulated output of Barrel Shifter using ModelSim.

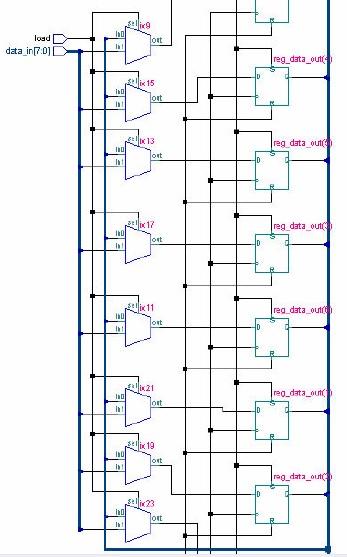

Synthesized Output

The synthesized output of the Barrel Shifter, obtained using Leonardo Spectrum Tool, is shown below:

Figure 2: Synthesized output of Barrel Shifter using Leonardo Spectrum Tool.

Advertisement

RF

RF