RAM and ROM Verilog Code Examples

Advertisement

This page covers RAM Verilog code and ROM Verilog code. It also provides a link that compares RAM vs ROM.

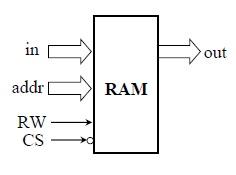

RAM Verilog Code

Following is the figure and Verilog code of RAM (Random Access Memory).

module RAM_code(out, in, addr, RW, CS);

output [7:0] out;

input [7:0] in;

input [3:0] addr;

input RW, CS;

reg [7:0] out;

reg [7:0] DATA[15:0];

always @(negedge CS) begin

if(RW==1'b0) //READ

out=DATA[addr];

else if(RW==1'b1) //WRITE

DATA[addr]=in;

else

out=8'bz;

end

endmodule

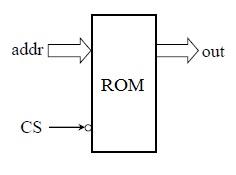

ROM Verilog Code

Following is the figure and Verilog code of ROM (Read Only Memory).

module ROM_code(out, addr, CS);

output[15:0] out;

input[3:0] addr;

input CS;

reg [15:0] out;

reg [15:0] ROM[15:0];

always @(negedge CS) begin

ROM[0]=16'h5601;

ROM[1]=16'h3401;

ROM[2]=16'h1801;

ROM[3]=16'h0ac1;

ROM[4]=16'h0521;

ROM[5]=16'h0221;

ROM[6]=16'h5601;

ROM[7]=16'h5401;

ROM[8]=16'h4801;

ROM[9]=16'h3801;

ROM[10]=16'h3001;

ROM[11]=16'h2401;

ROM[12]=16'h1c01;

ROM[13]=16'h1601;

ROM[14]=16'h5601;

ROM[15]=16'h5401;

out=ROM[addr];

end

endmodule

Advertisement

RF

RF