JESD204B and JESD204C Interface Advantages

Advertisement

This page explores the advantages of JESD204 interfaces, specifically JESD204B and JESD204C.

What is the JESD204 Interface?

In recent years, Analog-to-Digital Converters (ADCs) and Digital-to-Analog Converters (DACs) have seen significant improvements in speed and resolution. Connecting these ADCs/DACs with FPGAs/ASICs can be challenging. The JESD204 specifications were developed to address this interface requirement between converters and FPGAs/ASICs. It offers improvements over its predecessors, CMOS and LVDS, in terms of speed, size, and cost. The interface reduces pin count, facilitating smaller board designs. The JESD204 standard is also scalable to meet future needs.

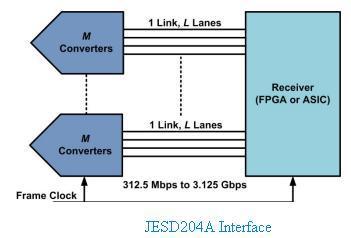

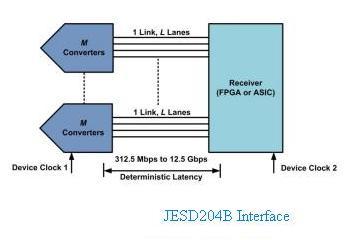

The JESD204 standard defines a multi-gigabit serial data link between converters and receiver devices like FPGAs/ASICs. Here’s a look at the evolution of the JESD204 standards:

- JESD204A: Published in 2008; Max Lane Rate: 3.125 Gbps; Encoding: 8B/10B

- JESD204B: Published in 2011; Max Lane Rate: 12.5 Gbps; Encoding: 8B/10B

- JESD204C: Published in 2017; Max Lane Rate: 32.5 Gbps; Encoding: 8B/10B, 64B/66B, 64B/80B

General Benefits/Advantages of JESD204 Interface

The following are generic benefits applicable to JESD204A, JESD204B, and JESD204C:

- Reduced/simplified PCB area

- Reduced package size

- Comparable power for large throughput

- Scalable to higher frequencies

- Simplified interface timing

- Standard interface

What is the JESD204C Interface?

The JESD204C interface offers several key features:

- Backward compatibility with JESD204A and JESD204B.

- Support for high megabit and gigabit data rates for applications like 5G cellular equipment, test equipment, medical devices, and military applications.

- Incorporates all features of JESD204B with added benefits.

- Supports single or multiple lanes, serial lane alignment and monitoring, and lane synchronization.

- Modular design for multi-device synchronization.

- Supports device subclasses: subclass-0 (no deterministic latency) and subclass-1 (uses SYSREF signal for deterministic latency).

- LEMC (Local Extended Multiblock Counter) for deterministic latency and multichip synchronization.

- Encoding: 8B/10B, 64B/66B, 64B/80B

- Scrambling and descrambling with polynomial: 1 + X39 + X58

- No FEC support

- MAC and PHY partitioning

Benefits/Advantages of JESD204C over JESD204B

JESD204C provides several advantages over JESD204B:

- Improved DC balance, clock recovery, and data alignment.

- Lower bit overhead (3.125%) compared to JESD204B (~25%).

- Supports CRC-12 for error detection within frames.

- Supports up to 256 frames in a multi-frame, compared to JESD204B (~32).

For complete information on JESD204 and its versions, refer to the standard specifications published on jedec.org.

Advertisement

RF

RF